Fast Versatile DMA

FastVDMA is a DMA controller designed with portability and customizability in mind.

Languages

Fast Versatile DMA

Copyright (c) 2019-2025 Antmicro

Overview

FastVDMA is a DMA controller designed with portability and customizability in mind.

Supported features

- Interrupts

- 2D transfers with configurable stride

- External frame synchronization inputs

Supported buses

- Data

- AXI4

- AXI-Stream

- Wishbone

- Control

- AXI4-Lite

- Wishbone

Dependencies

Because the controller is written in Chisel, it requires sbt, scala and java to be installed; additionally the tests require imagemagick.

Simulation

FastVDMA can be simulated as a whole but certain components can be tested separately.

You can simulate the full memory to memory design by running:

make testM2M

And the full stream to memory test by:

make testS2M

Each test run generates a .vcd file which can be opened using GTKWave or any other .vcd viewer.

Output files are located in a separate sub directories inside the test_run_dir directory.

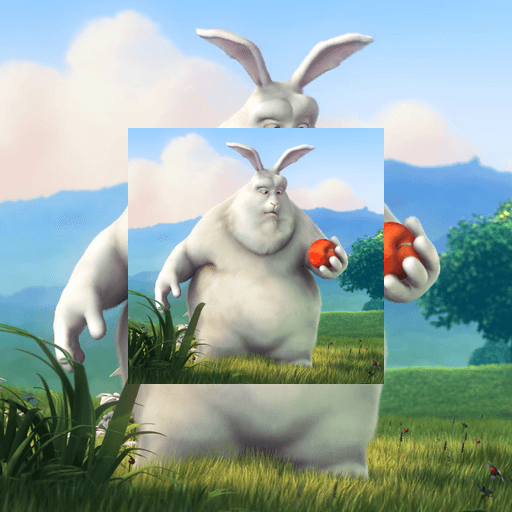

The full test should generate an outM2M.png/outS2M.png file demonstrating a 2D transfer with configurable stride. The resulting image should look similar to:

Synthesis

To generate a synthesizable verilog file either proceed with the default configuration by running:

make verilog

Or provide a valid configuration file with:

make CONFIG_FILE=<path_to_json_file> verilog

The generated file will be named DMATop$(configuration).v where configuration is chosen configuration of buses in the DMA. Verilog module will be named in the same manner.

See the documentation on how to provide custom configuration -- link here.

Source code structure

- src/main/scala/DMAController contains sources of the DMA controller

- src/test/scala/DMAController contains tests

Relevant projects

Nothing found

Apologies, but no results were found.